Administrando los recursos analógos (PSoC5LP)

Seguimos con el proyecto, esta vez tratando de mejorar el ruteo de los pines analógicos.

Como siempre, Cypress nos ofrece una buena AppNote referente al tema de Selección de pines para diseños analógicos.

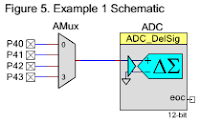

Podemos ver en el AppNote un ejemplo muy similar al nuestro, donde rutean 4 entradas analógicas con un AMux hacia la entrada de un SAR ADC:

Los pines seleccionados son P4[0], P4[1], P4[2] y P4[3], si abrimos el Analog Editor podemos ver que estos pines ocupan los Analog Globals: AGL[4], AGL[5], AGL[6] y AGL[7].

La asignación de dichos pines no es optima, vemos que se ocupan demaciados AG y no podremos rutear otras señales por estos paths usando dichos AG.

¿Qué podemos hacer para mejorar el ruteo?

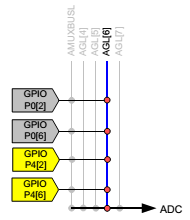

En la página 3 del AppNote podemos ver en totalidad el diagrama analógico interno del PSoC 5LP, y nos percatamos de lo siguiente:

Los GPIO 2[0], 2[4], 0[0] y 0[4] comparten un solo AG (AGL[4]) entonces si asignamos dichos pines como entradas para nuestro AMux solo ocuparemos ese AG, mejorando asi el ruteo analógico interno:

Algo muy similar tenemos en nuestro diseño, se eligieron al principio los pines 0[0], 0[1], 0[2] y 0[4] como entradas analogicas:

Si abrimos el Analog Editor podemos ver que tambien se ocuparon 4 AGs, AGL[4], AGL[5], AGL[6] y AGL[7] (cualquier parecido con el AppNote es mera coincidencia).

|

| Parte superior del diagrama |

|

| Parte inferior del diagrama |

Idealmente cambiariamos los pines a P0[0], P0[4], P4[0] y P4[4] y estaría listo pero esto no es posible con la CY8CKIT-059, la siguiente imagen nos ayudara a saber porque:

No tenemos P4 en los QFN de 68 pines, este integrado es el que tenemos en dicha tarjeta, ¿Qué podemos hacer entonces? Usar el P3!!!. Otra cuestion a tomar en cuenta seria el Capacitor de Bypass que necesita el SAR ADC, en la placa esta ubicado en el pin P0[4] para el SAR0 y P0[2] para el SAR1, entonces para que no intervenga debemos usar el SAR1, para asegurarnos de que el Analog Editor use el SAR1 debemos de lockearlo, click derecho en el componente y click en Lock to F(SAR, 1)

|

| SAR1 Lock |

Asi el Analog Editor sabrá que debe usar ese ADC SAR a la hora de compilar el programa. Ahora solo asignamos los pines de la siguiente manera:

|

| Asignación de pines |

Como vemos el Capacitor de bypass que elegimos es el del SAR1 que se encuentra en P0[2] para que no nos estorbe además de los pines de entrada analógicos P0[0], P0[4], P3[0] y P3[4] y los pines que usamos para debuguear el Basic Counter y la LUT.

Y asi queda el ruteo analógico interno:

Solo usamos el AGL[4] y AGR[4] y el SAR1, ahora solo tenemos que bloquear las rutas, click derecho sobre la ruta y seleccionamos la opción Lock route:

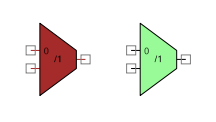

Podemos ver como las rutas pasaron a ser de un color negro solido y no punteado como antes de bloquearlas:

|

| Rutas bloqueadas |

Y al parecer es lo más que podemos administrar los recursos analógos internos del PSoC. Solo queda usar el DMA para sacar la conversión del ADC por el UART.

Comentarios

Publicar un comentario